# A REVIEW PAPER ON DESIGN OF FPGA BASED HIGH SPEED NOTCH FILTER USING PARALLEL

## **PROCESSING**

Miss.Pritigandha s. Mahure Dr. Pakaj aggrawal

Electronics and CommunicationElectronics and Communication

Engineering, Engineering, G H Raisoni Academy of G H Raisoni Academy of

Engineering and Technology, Engineering and Technology,

Nagpur, Maharashtra, India Nagpur, Maharashtra, India

Abstract— In this, we present a Field Programmable Gate Array (FPGA) based design and implementation of extremely high speed tunable IIR Notch filter. Here we will propose FPGA based Notch filter whose frequency is 1.2Gsps with the help of parallel processing. For speed up factor new and easy method of Pascal's Triangle is used to calculate multiplier coefficient for feed forward and feed backward section of extremely high speed Notch filter

*Keywords*—: Scattered Look Ahead Parallel process, Pascal Triangle, Tunable Notch filters, unfolding.

### I.INTRODUCTION -:

The Notch filter is used to Notch out particular frequency from input signal. The requirement of digital Notch filters to operate at extremely high clock frequency in the order of (Giga samples per second Gsps). We propose FPGA implementation of extremely high Speed Notch filter applying standard technique of parallel processing.

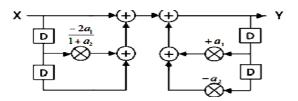

FIG1]. 2<sup>nd</sup> ORDER IIR NOTCH FILTER STRUCTURE

# DERIVE MULTIPLIER COEFFICINT USING PASCAL'S TRIANGLE METHOD:

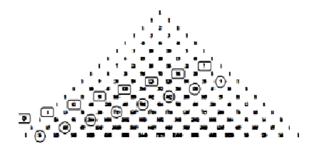

The coefficient of transfer function can be calculated by using this easy and new method. The values of coefficient can be calculated by subtracting values of square from circle. The first coefficient value is 16-0=1, The second coefficient value is 105-1= 104, The third coefficient value is 364-12=352. In this way coefficient of transfer function of filter is obtained.

FIG2]. PASCAL'S TRIANGLE TO DERIVE MULTIPLIER COEFFICIENT

# JOURNAL OF INFORMATION, KNOWLEDGE AND RESEARCH IN ELECTRONICS AND COMMUNICATION (ISSN 0975 – 6779, GIF: 01.6890 – SIF: 02.885)

## A FPGA BASED DESIGN OF EXTREMELY HIGH SPEED NOTCH [Parallel processing of IIR Notch filter]

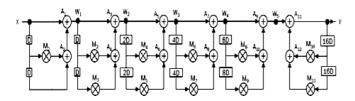

processing in the feedback loop the basic IIR Notch filter is decomposed with SLA16 as show in fig below. The 4- unfolded version of IIR Notch filter is as shown. It contains 6 stages, the Forward Stage and 1 Feed Backward

To introduce 16 or multiple of 16 for parallel

FIG3]. FULLY PIPELINED WITH SLA 16 DECOMPOSED IIR NOTCH FILTER

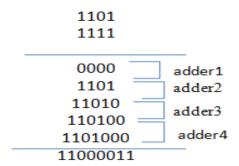

To create Notch filter we required ADDER and Multiplier. Consider multiplication of two four bit number.

WAVEFORM-:

A] SIMULATION FOR ADDER

## B] SIMULATION FOR MULTIPLIER

| G 🥠 je jediplorjni            | 0001111000111                           | 000011                 | 10000111 | 1        |        |          | Ξ    |     |       |       |        |                            | Ξ     |         | Ξ     |               | Ξ    |       |                |      |      |      | Ξ          |

|-------------------------------|-----------------------------------------|------------------------|----------|----------|--------|----------|------|-----|-------|-------|--------|----------------------------|-------|---------|-------|---------------|------|-------|----------------|------|------|------|------------|

| - 👌 e tulpierin l             | 0010100011110                           | uuuuuuu (0111100110110 |          |          |        |          |      |     |       |       |        |                            |       |         |       |               |      |       |                |      |      |      | _          |

| / k_milipler/dx               | 1                                       | Л                      | Л        | T        | Л      | Л        | Л    | Л   | Л     | π     | π      | Л                          | Л     | Л       | π     | Л             | Л    | Л     | π              | Л    |      | П    | Ī          |

| B. k. militier joutut         | 0000011100110                           | uuu                    |          |          |        |          |      |     |       |       |        | 00000111000011110001000000 |       |         |       |               |      |       |                |      |      |      |            |

| / Je_milipler/done            | 0                                       |                        |          |          |        |          |      |     |       |       |        | L                          |       |         |       |               |      |       |                |      |      |      |            |

| g / kjuliplorkjaljó           | 0111100011110                           | 00000                  | 00000    | 0        |        | 0011     | 101  | 101 | 10000 | 0000  | 0000   | 00000                      | 0000  | 01      | 10110 | 10010.        | 100. | 01011 | 100101         | 0100 |      | 100  | þ          |

| Bé kyndiplerkjal pob          | 000000000                               | 00000                  | 00000    | 0        |        | D000.    | 00.  | 00  | 0000  | 1110  | 0000   | 00000                      | 0000  |         | Ξ     |               | 00.  | 0000  | <b>1</b> 0000  | 110  |      | 000. | þo         |

| B de publisher in 2 lib       | 011110000111100                         | 00000                  | 00000    | 0        | 001    | . biii   | 111. | 111 | 0000  | 00000 | 000    |                            | 001.  | 111_    | 000   | 111).         | 111. | 0000  | <b>1</b> 00000 | 000  | 0011 | 011. | li         |

| G∱ kyndiplerkji2,neb          | 000000000                               | 000000                 | 00000    | 0        | 000    | . (000   | )00  | )00 | 0000  | 00000 | 000    |                            | Ξ     |         |       | 000.          | .bo  | 0000  | <b>(</b> 0000) | 000  | 000. | 000  | 00         |

| / hymiteleris.comy            | 0                                       | _                      |          |          | _      |          |      |     |       |       |        |                            |       |         |       |               |      | L     | L              |      |      |      | l          |

| / Jejudiplerje find com       | 0                                       | _                      |          |          |        |          |      |     |       |       |        |                            |       |         |       |               |      |       |                |      |      |      | _          |

| B. / Apulipher Apint presiden | 000000000000000000000000000000000000000 | 00000                  | 00000    | )))))))) | 1000   | . (DOD). | )00  | )00 | 0000  | 1111  | 0000   | 0000.                      | .000  | 000     | 000   | <b>)</b> 000. | .00. | 0000  | <b>\$</b> 0000 | 111  | 000  | 000  | <b>D</b> 0 |

| h julipler k gounter          | 4                                       | 7                      | 3        | 10       | 11     | 12       | 13   | 14  | 15    | t     | 1      | 2                          | 3     | 4       | 5     | ì             | 7    | 3     | 9              | 10   | 11   | 12   | 13         |

| 🔥 je politikerje jare         | 0                                       | _                      |          |          | _      |          |      |     |       |       | L      |                            |       |         |       |               |      |       |                |      |      |      | _          |

| B* kjuliplerkjal_complant     | 111100001111000                         | 111100                 | 01111000 |          |        |          | Ξ    |     | Ξ     |       |        |                            | Ξ     |         | Ξ     |               |      |       |                |      |      |      | Ξ          |

| B* kjuliplerkjn2,complnent    | 110001111001010                         | шш                     | www      | W [10    | 00)110 | 10100    | Ξ    |     |       |       |        |                            | Ξ     |         |       |               | Ξ    |       |                |      |      |      | Ξ          |

| B. d. publish public propincy | 111111000111001                         | шш                     | www      | www      | www    | JUUJ     |      |     |       | 11    | 111100 | 011110                     | 00111 | 1000000 | (00)  |               | Ξ    |       |                |      |      |      | _          |

#### CONCLUSION -:

FPGA based design and implementation

Methodology of extremely high speed tunable notch filter is presented. The concept of pipelining, retiming, unfolding and high-speed. A new efficient and easy technique has been used to calculate the multiplier coefficients of extremely high speed IIR notch

filter using PASCAL triangle.

#### **REFERENCES:-**

[1] Cornell Drentea, Modern Communications Receiver Design and

Technology, Artech House, Norwood, MA, 2010.

[2] Philip E Pace, Detecting and Classifying Low-Probability-Intercept

Radar, Artech House, Norwood, MA, 2004.

[3] Hirano, K.; Nishimura, S.; Mitra, S.;, "Design of digital notch filters,"

Circuits and Systems, IEEE Transactions on, vol.21, no.4, pp.540-546,Jul 1974.

[4] Dhar, K.K.;,"Very high speed real-time IIR digital filter structures:

suitable for VLSI implementation," Circuits and Systems, 1993., ISCAS

'93, 1993 IEEE International Symposium on, vol., no., pp.623-626 vol.1,

3-6 May 1993

# JOURNAL OF INFORMATION, KNOWLEDGE AND RESEARCH IN ELECTRONICS AND COMMUNICATION ( ISSN 0975 – 6779, GIF: 01.6890 – SIF: 02.885)

[5] Landry, R., Jr.; Calmettes, V.; Robin, E.; , "High speed IIR filter for

XILINX FPGA," Circuits and Systems, 1998. Proceedings. 1998

Midwest Symposium

[6] Azam, A.; Sasidaran, D.; Nelson, K.; Ford, G.; Johnson, L.; Soderstrand,

M.; , "Efficient pipelined tunable heterodyne notch filter implementation

in FPGAs," Circuits and Systems, 2000. Proceedings. ISCAS 2000

Geneva. The 2000 IEEE International Symposium on, vol.5, no.,

pp.373-376 vol.5, 2000

[7] Azam, A.; Sasidaran, D.; Nelson, K.; Ford, G.; Johnson, L.; Soderstrand,

$M.;\ ,\ "Single-chip tunable heterodyne notch filters implemented in$

FPGA's ," Circuits and Systems, 2000. Proceedings of the 43 rd IEEE

Midwest Symposium on, vol.2, no., pp.860-863 vol.2, 2000

[8] Yamada, M.; Nishihara, A.;,"High-speed FIR digital filter with CSD

coefficients implemented on FPGA," Design Automation

Conference,2001. Proceedings of the ASP-DAC 2001. Asia and South

Pacific, vol.,no.,pp.7-8, 2001

[9] Allred, D.J.; Huang, W.; Krishnan, V.; Yoo, H.; Anderson, D.V.;, "An

FPGA implementation for a high throughput adaptive filter using

distributed arithmetic," Field-Programmable Custom Computing

Machines, 2004. FCCM 2004.12th Annual IEEE Symposium on,

vol.,no.,pp. 324- 325,20-23 April 2004

[10] Lok-Kee Ting; Woods, R.; Cowan, C.F.N.; , "Virtex FPGA

implementation of a pipelined adaptive LMS predictor for electronic

support measures receivers," Very Large Scale Integration (VLSI)

Systems, IEEE Transactions on, vol.13, no.1, pp.86-95, Jan. 2005

[11] Abed, K.H.; Venugopal, V.; Nerurkar, S.B.; , "High speed digital filter

design using minimal signed digit representation," SoutheastCon, 2005.

Proceedings. IEEE, vol., no., pp. 105- 110, 8-10 April 2005

[12] Mirzaei, S.; Hosangadi, A.; Kastner, R.; , "FPGA Implementation of

High Speed FIR Filters Using Add and Shift Method," Computer

Design, 2006. ICCD 2006. International Conference on, vol., no.,

pp.308-313, 1-4 Oct. 2007

[13] Ying Li; Chungan Peng; Dunshan Yu; Xing Zhang; , "The

implementation methods of high speed FIR filter on FPGA," Solid-State

and Integrated-Circuit Technology, 2008. ICSICT 2008.

International Conference on, vol., no., pp.2216-2219, 20-23 Oct. 2008